Section: New Results

Highlights of the Year

Our work on accuracy evaluation and optimisation for fixed point arithmetic was presented during a tutorial "Automatic Fixed-Point Conversion: a Gateway to High-Level Power Optimization" at IEEE/ACM Design Automation and Test in Europe [77] .

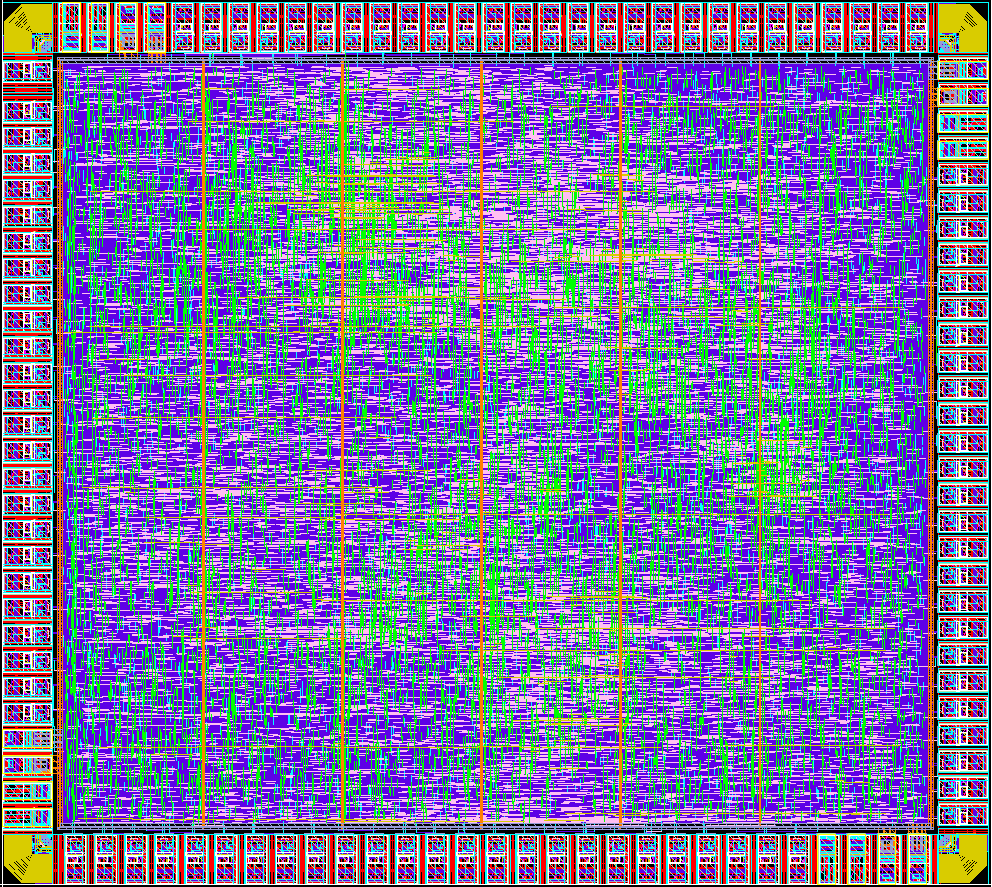

As a proof of concept of our research on improving efficiency of dynamic reconfiguration in FPGAs [47] [48] , the eFPGA (Figure 5 ) chip was designed and fabricated in 65nm CMOS technology. In the proposed and patented architecture [73] (EU patent), the configuration of the FPGA becomes independent from its placement and is moreover significantly compressed (up to ). This notion of Virtual Bit Stream allows for seamless partial and dynamic reconfiguration and for task migration.